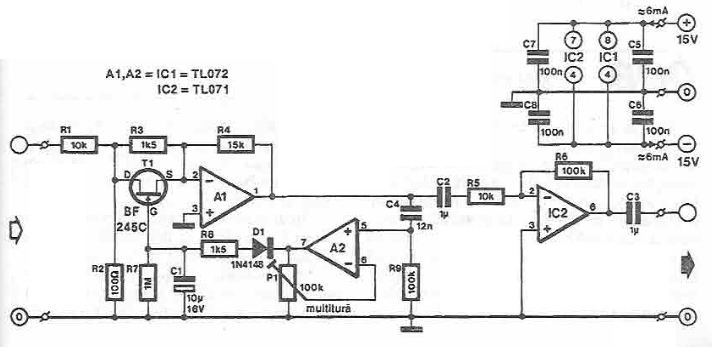

Electronic volume limiter circuit diagram project

This electronic volume limiter circuit provides an input signal less rich in harmonics and an additional amplification, within certain limits (as long as it does not distort compression

Field effect transistor T1 is used as a variable resistance that can vary from infinity to about 150 ohms. This resistance in parallel with R3 and R4 together with, determines Al gain. Without FET, gain of Al is about 20 dB.

Operational amplifier non-inverting amplifier A2 is connected to, whose gain can be varied by potentiometer P1.

Gain reduction is done gradually, as C1 must discharge through R7.

Because the internal resistance of T1 is influenced by voltage drain-source signal level must be kept as low as possible. It is therefore referred to input an attenuator R1-R2, which provides an attenuation of 40 dB, allowing the signals to a VEF not suffer more than 0.6% distortion. For input signals of a VEF the signal / noise is about 70 dB.

A1 and A2 amplification on attenuator compensates losses: total gain of the circuit, with T1 locked, is 0 dB.

Required voltage is ± 15 V and input current of the circuit will be 6 mA.

Add new comment